#### II B.Tech - I Semester – Regular Examinations - FEBRUARY 2022

### ELECTRONIC DEVICES AND AMPLIFIER CIRCUITS (Common for EEE, ECE)

| Duration: 3 hours                                                                  | Max. Marks: 70 |

|------------------------------------------------------------------------------------|----------------|

| Note: 1. This paper contains questions from 5 units of Syllabus. Each unit carries |                |

| 14 marks and have an internal choice of Questions.                                 |                |

| 2. All parts of Ouestion must be answered in one place.                            |                |

## <u>UNIT – I</u>

- a) With a circuit diagram, illustrate the operation of a 7 M common emitter amplifier and obtain its voltage gain expression.

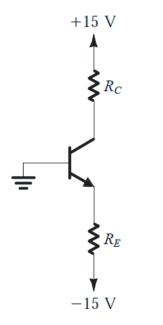

- b) Design a circuit similar to that shown in below figure 7 M except that now the power supplies are  $\pm 1.5$ V and the BJT has  $\beta =100$  and exhibits V<sub>BE</sub> of 0.8V at i<sub>c</sub>=1mA. Design the circuit so that a current of 2 mA flows through the collector and a voltage of +5V appears at the collector.

Page **1** of **4**

- 2. a) Compare common base (CB), common emitter (CE) 7 M and common collector (CC) configuration of a transistor. For CE configuration prove that  $I_C = \beta I_B + (\beta+1)I_{CO}$

- b) For a CE transistor amplifier circuit,  $R_1=50K\Omega$ , 7 M  $R_2=25K\Omega$ ,  $R_C=10K\Omega$ ,  $R_E=10K\Omega$ ,  $R_L=30K\Omega$ . Determine input and output impedances, current gain and voltage gain if transistor parameters are as follows  $h_{ie}=2K\Omega$ ,  $h_{fe}=100$ ,  $h_{re}=5x10^{-4}$ ,  $h_{oe}=25\mu$ S.

### <u>UNIT – II</u>

- 3. a) Analyze the MOSFET biasing technique using a large 7 M drain-to-gate feedback resistance  $R_G$ . Design the drain-to-gate feedback biasing circuit to operate at a DC drain current of 0.5mA. Assume  $V_{DD} = 5V$ ,  $k_n$ 'W/L=1mA/V<sup>2</sup>,  $\lambda = 0$ .

- b) What are the main constructional differences between a 7 M MOSFET and a BJT? What effect do they have on the current conduction mechanism of a MOSFET?

#### OR

- 4. a) With neat diagram analyze the operation of MOSFET 7 M in depletion mode and derive its current equations.

- b) Differentiate between current voltage relationships of 7 M the N channel and P channel MOSFET.

## UNIT-III

5. a) Obtain the expression for low frequency response of a 7 M MOSFET common source amplifier.

b) A MOSFET is to operate at  $I_D=0.1$ mA and is to have 7 M  $g_m=1$ mA/V. If  $k_n=50\mu$ A/V<sup>2</sup>. Estimate the required W/L ratio and the overdrive voltage.

#### OR

- 6. a) Analyze the internal capacitances of a MOSFET and 7 M hence draw the high frequency model of MOSFET.

- b) Estimate the mid band gain  $A_M$ , and the upper 3-dB 7 M frequency  $f_H$  of a MOSFET CS amplifier fed with a signal source having an internal resistance  $R_{sig}=100 \text{ k}\Omega$ . The amplifier has  $R_G=4.7M\Omega$ ,  $R_D=R_L=15k\Omega$ , ,  $g_m=1mA/V$ ,  $r_o=150k\Omega$ ,  $C_{gs}=1pF$  and  $C_{gd}=0.4pF$

# $\underline{UNIT} - IV$

- 7. a) Explain the MOS differential pair with common mode 7 M input voltage and specify the input common mode voltage range.

- b) Show that if all transistors are operated at an overdrive 7 M voltage  $V_{ov}$  and have equal Early voltages  $|V_A|$ , the gain is given by  $A_d = 2(V_A/V_{oV})^2$ . Estimate the gain for  $V_{ov}= 0.25$  V and  $V_A = 20$  V.

#### OR

- 8. a) Obtain input offset voltage of the MOS differential pair 7 M with necessary diagrams.

- b) An NMOS differential amplifier utilizes a bias current 7 M of 200  $\mu$ A. The device have V<sub>t</sub> =0.8V, W=100  $\mu$ m, and L=1.6  $\mu$ m, in a technology for which  $\mu_n C_{ox}$ = 90  $\mu$ A/V<sup>2</sup>. Find V<sub>GS</sub>, g<sub>m</sub> and the value of V<sub>id</sub> for full-current switching. To what value should the bias current be changed in order to double the value of V<sub>id</sub> for full-

current switching?

# <u>UNIT – V</u>

- 9. a) Compare the operating regions of Bipolar and MOS 7 M transistors.

- b) Interpret the current steering circuit using five 7 M MOSFET transistors and distinguish the current source and current mirror.

### OR

- 10. a) Explain the operation of MOS current steering circuit 7 M and mention its advantages.

- b) Show that for a MOSFET the selection of L and  $V_{ov}$  7 M determines  $A_0$  and  $f_T$ . In other words, show that  $A_0$  and  $f_T$  will not depend on  $I_D$  and W.